TREX Workshop: Code Tuning for the Exascale

TREX Workshop: Code Tuning for the Exascale

05-07 June 2023

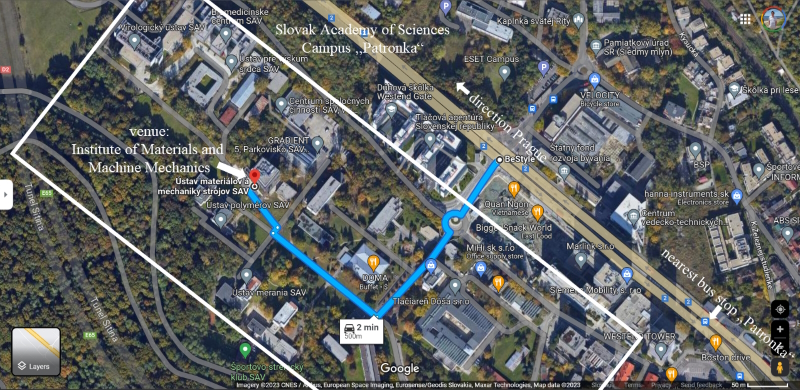

Slovak Academy of Sciences campus, Bratislava, Slovakia

Thank you for joining us! You can read the event highlights here and check the downloadable presentations.

Overview

The TREX project is pleased to host the “Code Tuning for the Exascale” as a physical workshop on June 05-07 in Bratislava, Slovakia.

The workshop is targeting specifically code developers and will be focused on code optimisation. Participants are encouraged to bring their own codes to learn about techniques, methods and solutions on how to improve them both in terms of performance and in terms of scalability across multiple platforms.

The workshop is co-organised by the TREX project and the Austrian, Czech and Slovak National Competence Centres for HPC.

The event will be organised in a mix of tutorials and training activities, focussing mainly on performance, power consumption, and energy efficiency in HPC systems and providing hands-on sessions on a series of codes and tools including TREX CHAMP code.

The language of the workshop will be in English. Full programme of the workshop will be available in the coming weeks.

What are the main goals of this workshop?

- Increasing practical experience in performance, power consumption, and energy efficiency in HPC systems.

- Helping participants to optimise codes to make sure the implementation match their HPC objectives;

- Provide hands-on experience with practical QMC simulations based on CHAMP code.

Draft programme

Day 1 - 05.06.2023

Advanced parallel programming – MPI+X: Modern HPC systems are clusters of shared-memory nodes and especially the pre-exascale and exascale systems are accelerated with one to several GPUs per node. While the Message Passing Interface (MPI) is the dominant model to parallelize across nodes, there is a need to combine MPI with other programming paradigms such as OpenMP to fully exploit shared-memory within the nodes and to be able to offload heavy compute task to the GPUs. In this one day tutorial, we will briefly cover MPI+OpenMP+OpenMP offloading.

We will explain how to properly tackle NUMA (non-uniform memory access) architectures and put a special focus on pinning. In the hands-on labs we will play around with affinity and the participants will get a good grasp about how pinning influences performance.

Content will be delivered by the team from the National Competence Centre for HPC in Austria.

Day 2 - 06.06.2023

Introduction to the fundamental concepts of parallel applications performance analysis, power consumption measurement, and energy efficiency evaluation in HPC systems. We will focus on the performance analysis process and methodology developed during the POP CoE project, followed by the mechanisms that today's computing hardware and systems provide in terms of monitoring and control of power and energy dissipation. The practical aspect of these principles will be shown during hands-on sessions.

Content will be delivered by the team from the National Competence Centre for HPC in Czech Republic.

Day 3 - 07.06.2023

Code performance analysis methodology and tools in practical application. We will review and analyze the major performance bottlenecks when optimizing an application at the node level: vectorization, code quality, locality and parallelism. We will demonstrate how our toolset MAQAO / ONE View (www.maqao.org) can first detect such bottlenecks and assess quantitatively their performance impact. Such a quantitative analysis is used for helping the code developer define an efficient optimization strategy. The presentation will be illustrated with real data coming from TREX applications. Finally hands-on sessions will allow attendees to test on their codes the power of MAQAO/ONE View Toolset.

Content will be delivered by the team from ECR/Li Parad (UVSQ/UPSaclay), TREX CoE member.

All topics will be covered in lectures as well as in practical hands-on sessions.

Prerequisites

- The workshop is targeting developers and advanced HPC users with experience in parallel programming and C and/or C++ and/or Fortran programming languages.

- Attendees are kindly requested to bring their own laptop.

Important information

Luxury Garni Hotel Brix - Stromová 32, Nove Mesto, 831 01 Bratislava, Slovakia

LOFT Hotel Bratislava - Stefanikova 4, 811 05 Bratislava, Slovakia

Hotel Matyšák - Pražská 15, 81104 Bratislava, Slovakia

Hotel Max Inn - Pri Suchom Mlyne 7, 81104 Bratislava, Slovakia

Ibis Bratislava Centrum - Zamocka Ul. 38, 81101 Bratislava, Slovakia

ÚMMS SAV, v. v. i. (Institute of Materials and Machine Mechanics, Slovak Academy of Sciences), Dúbravská cesta 9/6319, 845 13 Bratislava, Slovakia.

Local: Bratislava.

Speakers

- William Jalby, Université de Versailles-Saint-Quentin-en-Yvelines/UPSaclay, France

- Cedric Valensi, Université de Versailles-Saint-Quentin-en-Yvelines/UPSaclay, France

- Claudia Blaas-Schenner, VSC Research Center, TU Wien, Austria

- Ivan Vialov, VSC Research Center, TU Wien, Austria

- Tomáš Panoc, IT4Innovations, VSB – Technical University of Ostrava, Czech Republic

- Ondřej Vysocký, IT4Innovations, VSB – Technical University of Ostrava, Czech Republic

- Radim Vavřík, IT4Innovations, VSB – Technical University of Ostrava, Czech Republic

- Matej Špeťko – IT4Innovations, VSB – Technical University of Ostrava, Czech Republic